即将于2017年11月8日在国家会议中心举办的AI World 2017世界人工智能大会,我们请到硅谷著名企业家、IEEE Fellow Chris Rowen,科技创始人兼CEO陈天石,比特CEO詹克团,阿里云量子技术首席科学家施尧耘,以及体系结构华人代表学者、UCSB教授谢源,在AI Cloud会场就

【新智元导读】计算机体系结构顶会MICRO落下帷幕,内存相关工作最受关注,专用加速器结构的研究热度升温,量子计算也得到了大量关注。在神将网络和机器学习加速方面,这届会议也出现了新颖的工作。我们请到美国大学圣塔芭芭拉分校谢源教授课题组神经网络架构研究团队博士后胡杏,博士生李双辰、谷芃、李谷澍进行点评。

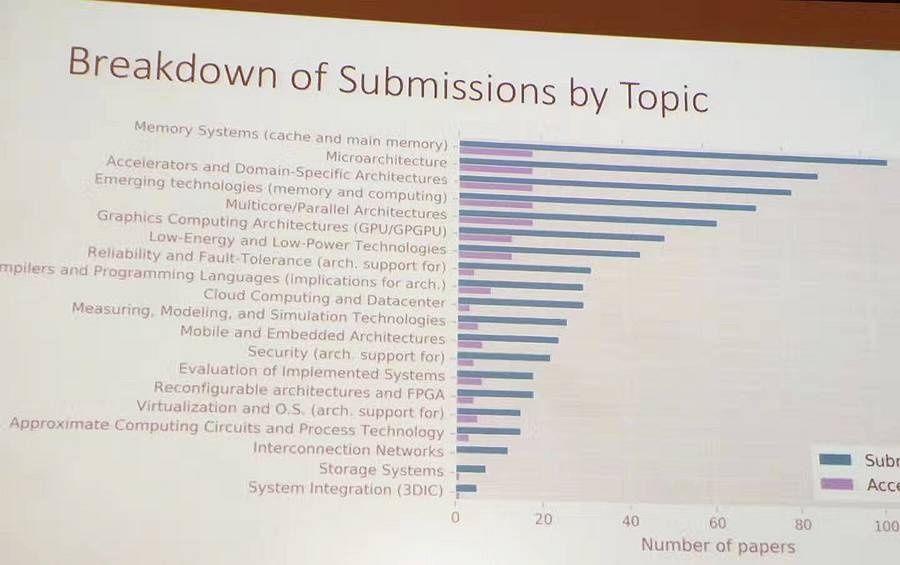

本次会议共接收326篇,收入61篇(录取率18.7%)。其中,内存相关工作无论是量还是收录量,依然稳居第一。

神经网络加速器工作依然有较高热度,但相对2016年ISCA和MICRO的盛况来讲,略有降温(4篇文章,其中包含一篇最佳论文提名文章)。

但是,对于专用加速器结构的研究热度有增无减(论文提交列位第三),包含了对数据解析,语音识别,图像去噪,非线性差分方程求解等不同应用。

值得一提的是,本届MICRO除了量子计算,还有一些让人耳目一新的工作,比如针对基于环保可降解材料的电路的架构设计,以及作为最佳论文提名之一的研究处理器设计对移动设备电磁干扰的影响。

这次MICRO会议华人学者也大放异彩:高光荣教授凭借对数据流编译器(dataflow compiler)的研究,荣获了B.Ramakrishna Rau大;谢源教授进入MICRO名人堂;最佳论文也由华人作为第一作者的工作斩获;第一作者为华人学者的论文占收录总数的1/4。

虽然从论文和接收数量上看略有降温,神经网络加速器和芯片设计仍旧是体系结构领域的研究热点。美国大学圣塔芭芭拉分校谢源教授课题组神经网络架构研究团队博士后胡杏,博士生李双辰、谷芃、李谷澍对MICRO 2017神经网络加速器工作进行了整理和点评。

摘要: 《DelftNN:通过突触向量消除和近计算数据分解,解决GPU上深度神经网络运行的瓶颈》论文由密歇根大学Scott Mahlke教授课题组,Lingjia Tang以及Jason Mars教授课题组合作完成。

目前的深度学习剪枝技术虽然减少了计算量,但是剪枝处理后的网络不能很好地映射到GPU架构上,通常不能有性能的提升。与此同时,目前的带宽优化技术集中于减少片外的带宽而忽略了片上带宽。为了解决这些局限性,本文提出了一个名为DeftNN的基于GPU的深度神经网络架构,从而自动且透明地提高深度神经网络在GPU上执行的性能。

DeftNN含有两种新的优化技巧:(1)突触向量消除技术:通过分辨深度神经网络中不重要的神经元和数据转换,以消除这些神经元的计算和数据传输,提高GPU的运行性能;(2)近计算数据分解技术:降低深度神经网络计算中片上数据传输的需求。通过分析6个最先进的深度神经网络模型,本文显示DeftNN在GPU上达到了平均2.1倍的加速。更进一步,如果在每个GPU核心引入额外的硬件单元去支持近计算数据分解,DeftNN的平均加速回升至2.6倍。

传统的神经网络剪枝技术虽然减少了存储和计算的需求,但其不规整的结构使得映射到GPU上运行的性能下降,主要由线程分支和访存不能聚集导致。针对这个问题,本文提出的突触向量消除技术能够在有效地压缩神经网络的同时,通过动态地将输入的数据映射到GPU能高效执行的结构,以规整的结构达到性能的提升。同时,通过运行6个典型的深度神经网络应用,本文观察到片上的访存带宽相比片外的带宽更加成为性能瓶颈。近计算数据分解技术能够有效地对片上的神经网络权重、输出进行压缩,从而缓解片上带宽的瓶颈问题。

摘要:《机器学习的横向扩展加速》论文由佐治亚理工的Hadi Esmaeilzadeh教授的ACT实验室完成。Hadi教授将于明年加入大学分校。该论文提出了CoSMIC全栈方法来构建可横向扩展的机器学习加速系统。在软件层,该工作首先基于并行梯度下降方法构建可分布式执行的软件系统,并提供基于高层次专用领域语言(DSL)的编程接口。根据这些抽象表达,CoSMIC可抽取出数据流图,进而进行加速器资源的规划布局,然后CoSMIC编译器实现操作与加速处理单元的映射。在硬件层,该工作设计硬件模板结构,从而可以生成优化架构来应对不同的并行梯度下降计算、聚合和更新的需求。同时,为了增加执行效率,该工作还在调度层进行优化,匹配硬件参数配置和软件算法需求。该论文在基于UltraScale+的FPGA平台上搭建了16节点的可扩展系统,并针对10种不同的机器学习算法进行了性能评估,从4节点扩展到16节点时,CoSMIC获得2.7x的性能提升而Spark获得1.8x的性能提升,相比于Spark方案,CoSMIC方法具有更好的可扩展性。

点评:现有工作主要关注单节点的加速方法,当数据愈多网络日益复杂的情况下,扩展问题迫在眉睫。这篇工作关注了横向扩展机器学习加速系统的关键问题和挑战:1)如何减少编程复杂度,避免过多参与硬件设计;2)如何设计定制化加速器来构建可扩展系统;3)如何提高分布式加速系统的软件系统性能和并实现优化映射来提高硬件资源利用率;这篇工作从软件算法、编程模型、编译器及调度器、硬件模版、电路设计等多个层次来构建了一个较完整的横向扩展加速系统。

摘要:《Bit-Pragmatic深度神经网络计算》论文来自大学,第一作者Jorge Albericio已加入NVIDIA。这篇论文在dadiannao基础上,结合神经网络冗余的特性,改进其对神经网络前向计算的加速。这篇论文沿袭该作者ISCA16的Cnvlutin(跳过数值为零的神经元)与MICRO16的Stripes(加速细粒度量化权重)两篇工作,并巧妙地将二者结合,实现了同时针对剪枝的大量为零的神经元以及对量化的低比特数权重的加速。具体来讲,该论文采用了串行乘,根据权重对神经元数值位移相加(stripes论文中的思路),来实现对量化为不同比特长度的权重的加速。在此技术上,该论文将神经元数值重新编码,再做移位相加的串行乘法,从而达到跳过数值为零的神经元计算的作用。同时,该论文还提出了如两级位移等方法,优化面积、功耗、存储访问等。实验结果显示对于8比特量化的神经元的网络,该方法比dadiannao快2.25倍,且有1.31倍的能效提升。

联合该课题组的三遍用于优化dadiannao架构的工作来看(ISCA16 Cnvlutin,MICRO16 Stripes,MICRO17 Bit-pragmatic),该系列工作完整的覆盖了神经网络中神经元的稀疏性,权重的可量化性,并在最终工作中将二者巧妙相结合,似乎已经做到了基于didiannao这种架构的AISC神经网络加速器的极致。

摘要:《CirCNN:使用分块循环的权重矩阵来加速和压缩深度神经网络》论文由塞浦路斯大学王言治教授课题组、南大学钱学海教授课题组以及林雪教授合作完成。该论文提出了一种基于分块循环矩阵的表达方法来压缩模型大小和加速模型速度。CirCNN使用分块循环表达的权值矩阵来进行训练和推断,并理论验证证明其性。分块循环矩阵是指改矩阵中每一行(列)都是其他行(列)的循环行(列)式。因此这种表达的存储复杂度从O(n2)降到O(n)。在计算时,使用傅里叶变换方法来对循环矩阵乘法运算进行加速,算法复杂度从O(n2)降到O(nlogn)。基于该算法,这篇论文还提出了CirCNN的体系结构设计,使用统一的DNN推断引擎来加速不同的网络结构(包括层数,大小,规模等等),其主要设计点包括通过傅里叶变换来加速分块循环矩阵计算、计算模块的流水线和并行性优化以及权值存储和内存管理优化等等。该论文在ASIC、FPGA和嵌入式GPU平台上验证了CirCNN,相比于现有工作能达到6-102x效能加速比。

现有模型压缩的方法虽然能大大减少存储复杂度,但可能影响网络模型的结构化特性,进而降低性能;此外,压缩率依赖于网络本身会提高控制复杂度。该论文基于分块循环表达的方法实现了结构化的压缩,并同时提高了训练和推断过程的性能。可贵的是本文还从理论上证明了该方法的可性,并分析了压缩率和准确度的关系。虽然不确定分块循环表达的训练过程速度如何,但是实验结果表明该方法确实具有很好的实用性,能大大加速执行时间和减少存储空间。

摘要:《DRISA:基于DRAM的可重构原地计算加速器》论文来由大学圣巴巴拉分校谢源老师研究组和三星内存研究组合作完成。这篇论文严格来说设计了一个可重构的较通用的加速器,但是以单比重神经网络为例子,作了深入的分析。该论文的设计目标为提供大规模片上存储同时提供高计算性能。为了达到这个目标,该项工作采用高密度的DRAM工艺打造高性能加速器。为了克服在DRAM工艺下复杂计算单元花费过多面积、功耗代价的问题,该论文仅仅设计了简单的布尔逻辑和移位电路,并串行迭代使用这些电路来计算加法乘法等复杂运算。同时由于定位在加速器设计而非可计算的系统内存,该设计以性能优化作为第一目标,有效的一些面积代价来换取更高的计算性能。总体而言,该结构拉近了计算和存储的距离,减小了数据搬移的能量消耗,并且充分利用了DRAM中大量的并行逻辑与更高的内部带宽,实现了对单比重神经网络这个示例应用的加速。

拉近计算和存储的距离是未来计算机架构的主要方向之一,更是神经网络计算所关注的方向。这篇论文将高密度的DRAM和高性能的计算单元设计到了一起,来实现这一目标。相比于Dadiannao等在处理器加速器芯片上集成更多eDRAM或SRAM的工作来说,该工作采用DRAM,比前者密度高出10倍;相比于内存计算工作,该工作摆脱了作为系统内存在设计上对面积、功耗等的要求,以设计高性能加速器为优化目标,从而得到了更好的性能。

摘要:《超导量子计算机中的一种实验性微架构》论文由荷兰代尔夫特理工大学K. Bertels教授课题组完成并获得了今年的最佳论文。该论文提出了一种微架构原型来实现对于量子计算机的灵活控制,和一套量子微指令集来实现精确时序下控制量子操作。量子计算机具有解决某些经典计算机难以解决的问题的能力,例如大整数的质因数分解和量子系统仿真。以往的量子计算机工程研究主要集中在两个方向:设计高层次编程语言和编译器来表示和优化量子算法,以及建造可靠的底层量子硬件。但是对于如何利用编译器的输出来完全地控制量子处理器的操作,相关的研究还比较少。该论文提出并构建了一种微架构原型来控制他们的超导量子处理器。这套微架构主要包括三个部分(1)一种基于codeword的事件控制机制,(2)基于队列的精确事件时序控制,和(3)一种灵活的多层次指令解码机制。该论文还设计了一套量子微指令集并应用在其架构中。该论文在FPGA上实现了微架构原型,并在一个单量子比特的量子处理器上做了实验。该微架构利用硬件加速了测量过程以实现实时反馈,解决了精确时序控制的问题,以及实现了灵活的量子操作模拟波形生成。

点评:量子计算机在原理上拥有解决一些在经典计算机上无决的问题的能力,从而在近几年越来越受到学术界和业界的关注。但是如何实现能够长时间相干的大量量子比特仍然在探索之中。以往关于量子计算机架构的研究通常基于尚未实现的大规模量子计算机的假设。这篇论文基于一个物理上已经实现的单量子比特处理器,设计了具有扩展潜力的微架构并解决了相关实践中的问题。这使得该论文的架构设计和实验结果十分扎实,令人信服。

摘要:《通过硬件管理的误差修正解决量子计算机指令带宽问题》论文由佐治亚理工大学Moinuddin K. Qureshi教授课题组,微软研究院Douglas M. Carmean,以及斯坦福大学博士生Zachary A. Myers合作完成。量子计算机由量子比特(qubits)和作为量子比特以及程序员之间接口的控制处理器实现。目前,误差修正主要由软件管理的机制实现,因此当量子比特的数量成规模增加时,需要极大的指令带宽,这将成为大规模量子比特计算机的瓶颈。本篇论文发现量子计算中99.999%的指令来源于误差修正,因此提出了一种名为“量子误差修正基质”(QuEST)的架构,用于将量子误差修正进行硬件管理。QuEST使用了一个专用的可编程微编码的引擎,持续不断地对误差修正相关的指令流进行重复。QuEST需求的指令带宽与活跃的量子比特(通常远小于整个量子比特数量的0.1%)成正比而不是与整个量子比特的数量成正比。进而,这篇文章分析了面积和热约束下QuEST的有效性,并提出了一种使用典型量子容错码(QECC)执行模式的可扩展的微架构。本文的分析显示,对于几种重要量子计算负载,QuEST能够有效地减少指令带宽5个数量级,同时确保确定性的指令执行。除此以外,本文作者观察到容错量子指令同样有巨大的指令带宽需求,因此扩展了QuEST增加了对这些指令的硬件支持。综上,QuEST能达到8个数量级的指令带宽的减少。

本文发现误差修正指令是量子计算机向大规模扩展的一个瓶颈,其根本原因是软件管理误差修正指令的方式,会导致误差修正指令带宽随量子比特的数量呈线性增长关系。本文提出将软件管理的方式变为硬件管理的方式,因此构建了一个量子计算机的控制架构(QuEST),可以在软件不参与的情况下连续地运行误差修正指令。进一步地,利用误差修正码的局部性和量子运行模型的原理,QuEST可将指令带宽减少5个数量级。同时本文将误差修正指令和容错指令分离,使得容错逻辑指令可以被缓存,进而一共使得指令带宽降低了8个数量级。

摘要:《超导量子计算机中经过优化的表面码通信》论文由大学Frederic T. Chong教授课题组和普林斯顿大学的Margaret Martonosi教授课题组合作完成。该论文设计了一系列编译,调度和网络模拟的工具,对于两种已有的量子纠错表面码进行了评估。由于量子比特本身对于噪声以及量子门操作的精度问题,大规模的量子计算机必须要对量子比特使用纠错编码。据估计,量子纠错编码使用的量子比特将占到总数的90%。所以,设计合适的量子纠错编码机制对于成功的量子计算机十分关键。该论文使用了应用-系统-技术的联合设计方法,设计了一套端到端的可扩展的软件工具链,来把用高级语言表示的量子程序,综合到物理级别的电路和布局上。针对目前最有潜力的量子纠错码,表面码,该论文把表面码通信中的静态“辫”调度问题从3维的拓扑转换问题,为2维的静态路由问题,通过过度的使其可以应用在大规模量子电路的设计中。该论文还发现,表面码中基于“辫”的通信虽然对于延时不,基于量子传态的通信由于可以预取,在可以高度并行化的量子算法中效果更好。

量子纠错编码是大规模量子计算机设计中的关键问题之一。该论文针对表面码这一种非常有潜力的纠错编码,对未来大规模量子计算机的设计方式进行了探索和模拟,并在模拟的结果中发现对于以往对于表面码通信的认识的不全面之处。该论文的结果对于未来量子计算机的发展是很具有指导意义的。

11月8日, AI World 2017世界人工智能大会将特设 AI Cloud分论坛,阿里云量子技术首席科学家施尧耘开讲《量子智能》,敬请关注。

大纲:人类智能是经典的还是量子的?如果是经典的话,基于量子信息技术的智能比人类智能强多少?当大规模量子计算机诞生时,这个差距又意味着什么呢?我将和大家一起讨论量子信息技术对智能的意义。

施尧耘,1997年本科毕业于大学计算机科学与技术系,随后在美国普林斯顿大学计算机系师从“图灵”得主姚期智院士研究量子信息科学,并于2001年获得博士学位。在理工学院量子信息研究所短暂的博士后研究后,他赴美国大学电子与计算机系执教、研究,历任助理教授、副教授、正教授。施教授的研究涉及量子信息科学的多个方向,比如量子计算复杂度、量子系统的经典模拟、量子密码学等。他的研究包括多个相应方向中最具代表性的工作;比如在Device-Independent量子密码学中取得了被认为突破性的进展。2017年6月,施尧耘入职阿里巴巴集团,出任阿里云首席量子技术科学家,筹建地处杭州、、西雅图的阿里耘量子实验室(AQL)。同时,施教授正在协助CTO张建锋筹划全面提升阿里巴巴的研究力量,并于近日代表阿里巴巴出任浙江省之江实验室副主任。

推荐:

删除。

删除。

网友评论 ()条 查看